Intelligente NAND Flash-Speicher für smarte Geräte

Die Nachfrage nach NAND-basiertem Flash-Speicher steigt, denn immer mehr Anwendungen in den Bereichen Consumer, Mobilfunk, Automotive, Industrie und Internet der Dinge (IoT) kommen zum Einsatz. Toshiba hat im Jahr 1984 den NAND-Flash-Speicher eingeführt. Seitdem hat sich dieser Markt rasant weiterentwickelt.

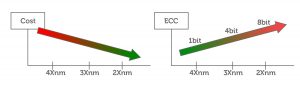

Fortschrittliche Prozesstechnik bei NAND Flash sorgt für sinkende Kosten und steigenden ECC-Aufwand (Bild: Toshiba Electronics Europe GmbH)

Die NAND-Speicherdichte hat seit ihrer Einführung vor über 30 Jahren um mehr als das 2000-fache zugenommen: In diesem Zeitraum wurden die Strukturgrößen durch moderne Halbleiterprozesstechnik von 700nm auf 15nm verkleinert und neue Zellenarchitekturen eingeführt. Hinzu kommt ein erheblicher Preisverfall pro Gbit, der schneller vonstattengeht als die Erhöhung der Speicherdichte. NAND wird somit für zahlreiche Anwendungen das Speichermedium erster Wahl. Während die Kosten pro Bit weiter sinken, ist der Übergang zu neuesten Technologien und Prozessknoten nicht immer ganz einfach: Eine der wesentlichen Herausforderungen beim Einsatz neuester Raw-NAND-Speicher ist die Umsetzung einer leistungsfähigen Fehlerkorrektur (ECC; Error Correction Code), die in Speicher-Controller integriert werden muss. Dabei findet ein ständiges Wettrennen mit der Technologie statt, bei dem häufig auf den passenden Controller gewartet werden muss. Bei Single Level Cell (SLC) NAND bis zu einem 43nm-Prozess ist z.B. nur 1Bit ECC pro 512Byte Speicher erforderlich. Dieser Wert erhöht sich bei einem 24nm SLC NAND auf 8Bit ECC pro 512Byte. Der Übergang von 43nm Raw SLC NAND auf 24nm Raw SLC NAND würde demnach die Leistungsfähigkeit senken, wenn nicht eine fortschrittliche Controller-Technik angewendet wird.

Fortschrittliche Prozesstechnik bei NAND Flash sorgt für sinkende Kosten und steigenden ECC-Aufwand. (Bild: Toshiba Electronics Europe GmbH)

Wear Levelling: Speicherblock-Verschleiß ausgleichen

Wird NAND-Flash mit immer kleineren Prozessknoten hergestellt, werden auch die Zellen immer kleiner, und deren Ausdauer und Zuverlässigkeit kommt mit ins Spiel. Desweiteren gibt es NAND-Zellen, die mehrere Bits speichern können. SLC NAND kann 1 Bit pro Zelle speichern, Multi-Level Cell (MLC) NAND kann 2 Bits pro Zelle speichern, und Triple Level Cell (TLC) NAND speichert 3 Bits pro Zelle. Davon ist jedoch die Schreib-/Lösch-Ausdauer betroffen: SLC unterstützt ca. 60.000 Zyklen, MLC 3.000 und TLC 500 Zyklen, vorausgesetzt der gleiche ECC-Algorithmus wird angewendet. Da NAND-Speicherblöcke verschleißen können, wird jede NAND-Speicherstelle mit einer Obergrenze an Schreibvorgängen bestimmt. Wear-Levelling-Algorithmen müssen ebenfalls in den NAND-Controller integriert werden, um die gleichmäßige Nutzung der Speicherstellen zu garantieren. Bei der Berechnung der System-Lebensdauer über die NAND-Zuverlässigkeit muss beachtet werden, dass die Speichermanagement-Funktionen mehr Schreibvorgänge verursachen, als ursprünglich zu schreibende Bits vorhanden sind. Der Grund: Speichermanagement-Funktionen können auch Datenübertragungen von einem Speicherort auf einen anderen umfassen, was zum mehrfachen Beschreiben von Zellen mit zu speichernden Daten führt. Während das Schreiben oder Programmieren eines NAND seitenweise erfolgt, finden Löschfunktionen blockweise statt; die Blöcke enthalten mehrere Seiten. Um einen Block für das Löschen vorzubereiten, werden die zu behaltenden Daten zuerst in andere Blöcke kopiert. Diese Seitenumbesetzung oder Page Shuffling vor dem Löschen eines Blocks wird Garbage Collection genannt.

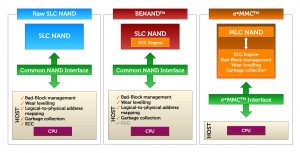

Um einen Block für das Löschen vorzubereiten, werden die zu behaltenden Daten zuerst in andere Blöcke kopiert. Diese Seitenumbesetzung oder Page Shuffling vor dem Löschen eines Blocks heißt Garbage Collection. (Bild: Toshiba Electronics Europe GmbH)

Den Controller entlasten

Bei vielen bestehenden Anwendungen, die SLC NAND nutzen – z.B. in der Industrieelektronik, Automobilelektronik und Kommunikationsprozessoren -, ist die 1-Bit-ECC in die Host-Software integriert, ohne die Leistungsfähigkeit merklich zu beeinträchtigen. Der Übergang zu einem aktuellen Speicher, der eine 4-, 8- oder sogar 24-Bit-ECC erfordert, erhöht die Prozessorlast erheblich und verringert somit die Leistungsfähigkeit. Um dies zu verhindern, werden NAND-ICs mit integrierter ECC bevorzugt. Toshibas BENAND (Built-in ECC NAND) ist eine solche Lösung und entlastet den Host-Prozessor um die ECC, ohne einen zusätzlichen Hardware-Controller zu erfordern. Die Lösung nutzt die etablierte NAND-Schnittstelle und ist kompatibel zu Raw SLC NAND Flash bezüglich Befehlssatz, Speicherbetrieb, Gehäuse und Anschlussbelegung. Das Host-System übernimmt das Bad-Block-Management, Wear Levelling, Adresszuordnung und Garbage Collection genauso wie bei Raw SLC NAND. Die Speicher stehen mit Kapazitäten von 1 bis 8Gb in den Standardgehäusen TSOP-I-48-P und 63-Ball-BGA zur Verfügung, die anschlusskompatibel zu den gängigen SLC-Gehäusen sind. Eine kleine 6,5mmx8,0mm 67-Ball-BGA-Version ist ebenfalls erhältlich, um neue Designs mit beengten Platzverhältnissen zu unterstützen. Die kompatiblen Anschlüsse und Gehäuse von Raw SLC NAND und BENAND erlauben einen direkten Austausch beim Aufrüsten auf neueste Flash-Speicher. Toshiba als Hersteller hilft Anwendern dabei, die Speicher in bestehende und neue Designs zu integrieren. Damit lassen sich die Vorteile neuester Flash-Speichertechnik nutzen, ohne teure Systemänderungen durchführen oder weiterhin veraltete Technik einsetzen zu müssen.

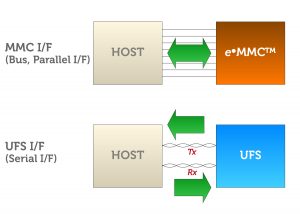

Die nächste Generation von Universal Flash Storage (UFS) soll Geschwindigkeiten von 5,8/11,6Gbps erreichen und sich in Multi-Lane-Lösungen implementieren lassen. Daten lassen sich dann über den seriellen Bus in Uplink- und Downlink-Richtung gleichzeitig übertragen. (Bild: Toshiba Electronics Europe GmbH)

NAND-Controller werden überflüssig

e?MMC NAND geht bezüglich der Speicherverwaltung oder Memory Management noch einen Schritt weiter als die angesprochene Lösung: NAND Flash und der Controller-Chip werden zusammen in einem Gehäuse verbaut. Die Bausteine entsprechen den JEDEC-Standards und kommen in Smartphones, Tablets, Set-Top-Boxen, TV-Geräten und in Industrierechnern zum Einsatz. Der Embedded Controller führen Funktionen wie Fehlerkorrektur, Wear Levelling und Bad-Block-Management aus und sorgen für den korrekten Betrieb des NAND-Speichers. e?MMC-Speicher basiert auf MLC NAND und vereint Raw MLC NAND mit einem NAND-Controller. Um beim Hochgeschwindigkeits-Datenaustausch die Zuverlässigkeit des Speichers zu erhöhen, kann managed MLC einen pseudo Single Level Cell (pSLC)-Modus nutzen, der SLC NAND emuliert. Dabei wird nur ein Bit in jeder MLC-Zelle gespeichert, und Daten lassen sich zehn Mal häufig austauschen als im Standard-MLC-NAND-Betrieb – bei vergleichbarer Zuverlässigkeit. Dies ist vor allem in Anwendungen wie Set-Top-Boxen von Vorteil, um Live-TV-Übertragungen zu pausieren, wobei Daten regelmäßig überschrieben werden. Der pSLC-Modus muss während der ersten Initialisierung aktiviert werden; der NAND-Controller verwaltet dann den MLC-Speicher wie gewohnt. e?MMC mit hoher Speicherdichte kann Interleaving nutzen, was die Leistungsfähigkeit durch paralleles Adressieren mehrerer Regionen erhöht. Bei Schreib- und Löschvorgängen befindet sich der NAND-Speicherbus im Betriebsmodus und muss auf eine Antwort warten. Erhält der integrierte NAND-Controller Zugriff auf einen anderen NAND-Chip oder ein separates NAND-Register bzw. einen separaten NAND-Bus, sind mehrere Zugriffe – wie Lesen, Schreiben und Löschen – möglich. Die Schnittstelle für e?MMC-Produkte ist durch das JEDEC-Konsortium standardisiert, um Interoperabilität zwischen den Produkten verschiedener Hersteller zu garantieren. Die e?MMC-Schnittstelle besteht aus einem parallelen 8/4/1-Bit-Datenbus und einigen wenigen Steuersignalen. Im Gegensatz dazu sind Raw-NAND-Schnittstellen nicht standardisiert. Sie verwenden einen parallelen 8Bit-Datenbus und wesentlich mehr Steueranschlüsse. Die neuste Version des JEDEC-Standards e?MMC v5.0 definiert eine Hochgeschwindigkeits-Schnittstelle (HS400) um die Anforderungen leistungsfähiger Systeme zu erfüllen. Sie umfasst auch einen Update-Vorgang, über den sich eine neue e?MMC Device Controller Firmware installieren lässt, sobald sich das Produkt im Einsatz befindet. Eine Sleep-Benachrichtigungsfunktion ermöglicht den sicheren Übergang in stromsparende Sleep-Modi. Eine wichtige Funktion jeder Version ist die Rückwärtskompatibilität zu e?MMC-Bausteinen, die früheren Standards entsprechen. Somit bietet die neue v5.0-Anschlussbelegung eine höhere Leistungsfähigkeit und ist gleichzeitig rückwärtskompatibel.

Einsatz in Highend- Smartphones und Tablets

Wie bei allen Digitalbausteinen zeigt sich auch bei Speicher-ICs ein stetiger Trend hin zu mehr Leistungsfähigkeit und einem geringeren Stromverbrauch in immer kompakteren Gehäusen. Toshiba fertigt sein e?MMC Flash im 15nm-Prozess, um diese Forderungen zu erfüllen. Ebenso besteht Bedarf, die Lebensdauer älterer Produkte zu verlängern. BENAND erfüllt diese Forderung und bietet aktuelle NAND-Technik, ohne die Controller-Hardware aufrüsten zu müssen. Auch ein größerer Betriebstemperaturbereich für Produkte mit e?MMC NAND Flash wird zunehmend gefordert. Der Standard-Betriebstemperaturbereich für e?MMC in Consumer-Elektronik reicht von -25 bis +85°C. Der Hersteller bietet aktuell Bausteine, die für den industriellen und AutomotiveInfotainment-Bereich ausgelegt sind und einen Temperaturbereich von -40 bis +85°C unterstützen. In Zukunft werden Highend-Smartphones und Tablets zu den ersten Geräten zählen, die nach e?MMC mit dem neuen Speicherformat UFS ausgestattet werden. Universal Flash Storage (UFS) befindet sich derzeit noch in der frühen Phase der Serienfertigung. Mit anfänglichen Datenübertragungsraten von 300MB/s oder 2,9Gbps Single Lane zielen die Bausteine auf hochleistungsfähige Consumer-Elektronik. Die nächste Generation dieses Speicherformats soll dann Geschwindigkeiten von 5,8/11,6Gbps erreichen und in Multi-Lane-Lösungen implementiert werden. Daten lassen sich dann über den seriellen Bus in Uplink- und Downlink-Richtung gleichzeitig übertragen. Entwickler Smart Devices verlangen intelligenteres, schnelleres NAND Flash mit höherer Speicherdichte, das rückwärtskompatibel ist und sich einfach integrieren lässt. Mit seiner umfangreichen Erfahrung im Bereich NAND Flash und Controller bietet Toshiba zuverlässige und hochleistungsfähige Speicherlösungen für die heutige, zukünftige und länger bestehende Geräte.