Schneller durch den Designprozess

Verifikationsläufe beanspruchen zumeist viel Zeit und bremsen so die Designentwicklung. Mit einem neuen physikalischen Verifikationstool versucht Mentor dies nun zu ändern. Damit haben Kunden die Möglichkeit ihre Designs um Wochen schneller auf den Markt zu bringen. Hier eine Kurzvorstellung des Tools.

Calibre RealTime Digital soll durch Zusammenarbeit mit gängigen kommerziellen Place-and-Route-Umgebungen Correct-by-Calibre-Routing gewährleisten und Designteams dabei helfen, den Signoff von ICs um Wochen zu verkürzen. Das Verifikationstool ist das Schwesterprodukt des Calibre RealTime Custom Tools, das 2011 für kundenspezifische IC-Designabläufe eingeführt wurde. Mit Schwerpunkt auf dem digitalen Full-Chip- und Block-Level-Markt, eignet sich das Calibre-RealTime-Digital-Tool u.a. für Teams, die hauptsächlich Asics und SoCs für eine breite Palette von Endprodukten wie Mobiltelefone, Automobile, drahtgebundene und drahtlose Infrastrukturgeräte sowie eine Vielzahl von industriellen und kommerziellen Anwendungen entwickeln.

Iterationen reduzieren

Das neue Tool hilft Designteams, ein gemeinsames Problem im letzten Schritt des Designprozesses zu lösen. Nach der Platzierung und dem Routing senden die Designteams ihre Entwürfe durch einen vollständigen DRC- (Design Rule Check) Verifikationslauf. Dieser kann bei einem Design mit Milliarden von Transistoren mehrere Stunden dauern. Frühe Verifikationsläufe decken oft Probleme im Design auf, die behoben werden müssen, damit sie den Fertigungsregeln der Foundry entsprechen. Die Designteams gehen dann zurück in ihre Place-and-Route-Tools, um die Probleme zu beheben. Anschließend führen sie erneut einen vollständigen DRC-Lauf durch. Dabei stellen sie oft fest, dass ihre Korrekturen zusätzliche Fehler verursachen, die zu noch mehr Iterationen und Verzögerungen führen, bevor sie schließlich zu einem korrekten fertigungsgerechten Design konvergieren.

Signoff-Zeitplan deutlich verkürzen

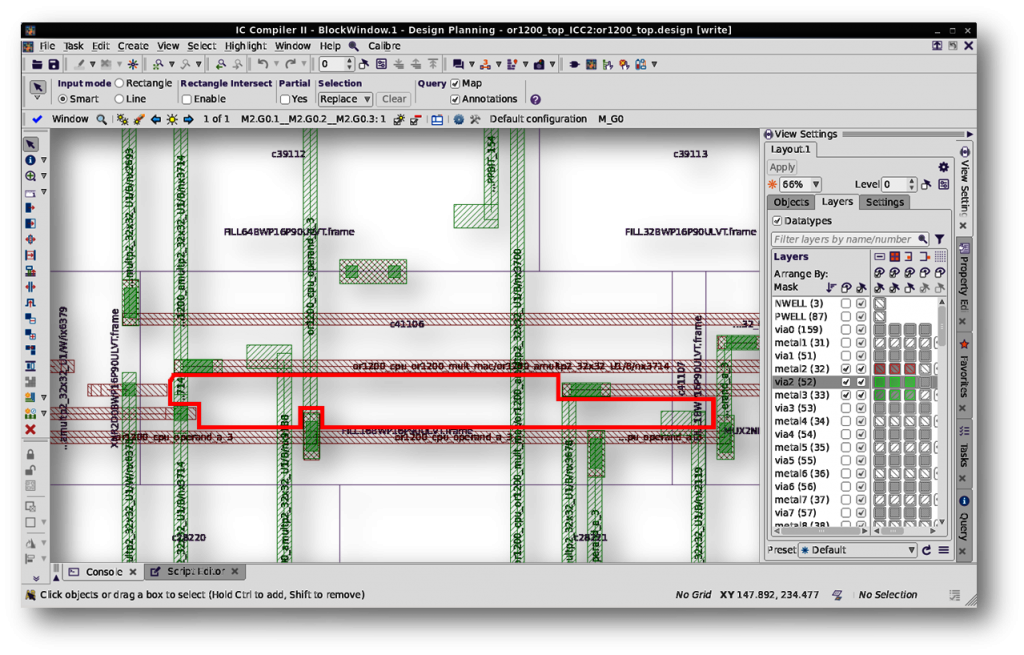

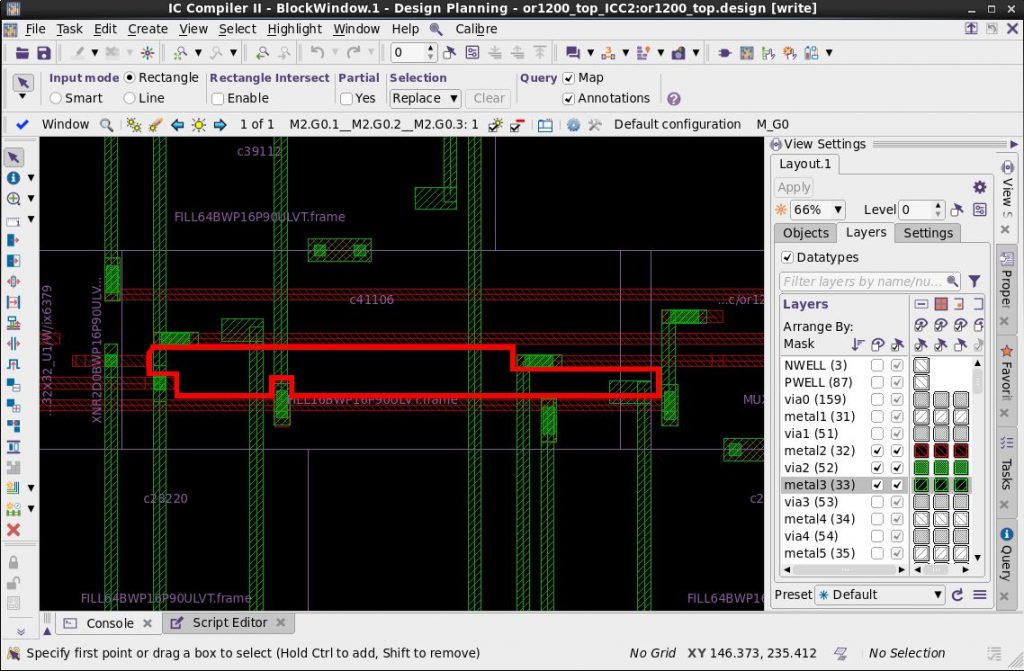

Das Tool hilft bei der Lösung dieser Probleme, indem es mit Place-and-Route-Tools zusammenarbeitet. Da die Designteams die nach vollständigen DRC-Läufen entdeckten Verstöße mit Place-and-Route beheben, können sie kleinere Änderungen vornehmen und so DRC-Verletzungen beheben, ohne zusätzliche Verstöße zu verursachen – ergo ‚Correct by Calibre‘. Erreicht wird dies, indem kleine Änderungen vorgenommen und benutzerdefinierte, kleinere und lokale DRC-Läufe durchführt werden, um sicherzustellen, dass die Verstöße sich beseitigen lassen. Kürzere Iterationen während des Debuggens reduzieren die Gesamtzahl der vollständigen Chip-Iterationen und ermöglichen es den Entwicklern, Designzyklen drastisch zu verkürzen und schneller auf den Markt zu kommen. „Das Tool ist ein Beschleuniger für unsere bestehenden physikalischen Verifikationsstrategien, der sich nahtlos in unsere Designabläufe einfügt“, erklärt Weikai Sun, Associate Vice President of Engineering bei Inphi. „Wir erwarten, dass sich unser Signoff-Zeitplan um Wochen verkürzen lässt.“ „Calibre RealTime Digital ist eine Lösung, die auf Kundenwünschen basiert“, sagt Joe Sawicki, Vice President und General Manager der Design-to-Silicon-Division von Mentor. „Das Tool kann Designteams, die Systemchips mit jedem digitalen Verfahren entwickeln, Zeit und Mühen sparen.“