DSP-Architektur verlängert die Batterielebensdauer

Beim Vorantreiben intelligenter Innovationen, die die Interaktion zwischen Mensch und Technik durch intelligente, dynamische Verarbeitung verbessern, geht es nicht ohne industrielle Technik. Leider sind diese intelligenten Innovationen mit einer Reihe von Herausforderungen verbunden, die es zu bewältigen gilt, bevor sich Innovationen in Produkte umsetzen lassen. Eine dieser Herausforderungen besteht darin, das Streben nach maximaler Performance und geringstmöglichem Stromverbrauch miteinander in Einklang zu bringen. Eine weitere Herausforderung stellt die Realisierung tragbarer, für den Batteriebetrieb geeigneter Systeme dar.

Kommerzielle Technologie revolutioniert die Portabilität durch Wearables, die die Interaktion des Konsumenten mit seiner Umgebung aufwerten. Derartige Geräte dienen vorwiegend dazu, die um den Anwender herum gesammelten Daten zu verarbeiten, zu analysieren und zusammenzufassen. Ebenso wie in der industriellen Technik besteht das übergeordnete Ziel hier darin, ein Höchstmaß an Leistungsfähigkeit zu erzielen und gleichzeitig mit möglichst wenig Energie auszukommen, damit Batteriebetrieb möglich ist. Entwickler haben grundsätzlich die Auswahl unter einer Vielzahl von Prozessorarchitekturen, jedoch ist es in hohem Maße die Anwendung, die bestimmt, welche Architekturen in Frage kommen. Je intelligenter die Techniken für Industrie- und Consumer-Anwendungen werden, umso mehr liegt der Schwerpunkt auf Analysen zur Bereitstellung von Ergebnissen. Bei diesen Analysen handelt es sich zumeist um weitgehend parallele mathematische Berechnungen, für die sich DSP-basierte Architekturen optimal eignen. DSP-Architekturen bringen beste Voraussetzungen für das parallele Wesen von Datenmanipulationen mit und enthalten leistungsfähige Recheneinheiten. Sie sind somit die beste Möglichkeit, die aktive Leistungsaufnahme zu senken und dadurch die Batterielebensdauer zu verlängern.

Das Innere von DSP-Architekturen

DSP-Architekturen ermöglichen die intelligente Auswertung von Daten, die von grundlegender Bedeutung für den Industrie- und Wearable-Markt sind, denn sie können vielfältige Algorithmen mit hoher Geschwindigkeit und vorhersagbarer Latenz verarbeiten. Hinter diesen Anforderungen steht die Erwartung der Anwender, in Echtzeit nützliche Informationen von dem betreffenden Gerät zu bekommen. Damit diese Echtzeitfähigkeit erreicht und gleichzeitig sparsam mit der Energie aus der Batterie umgegangen werden kann, muss die Architektur von Wearables kurze, vorhersagbare Latenzzeiten unterstützen, die eine zeitnahe Bereitstellung der jeweiligen Informationen zulassen. DSP-Cores erfüllen die Latenz-Anforderungen mithilfe vorhersagbarer Datenpfade und vorgeschalteter Virtual-Memory-Manager, die in nicht-deterministischen Systemen verbreitet eingesetzt werden. Der gesamte Datenpfad ist auf das Streamen von Daten mit geringstmöglicher Latenz ausgelegt. Reduziert sich die Latenz, muss der DSP weniger Zeit mit dem aktiven Koordinieren des Datenflusses verbringen, sodass der Batterie weniger Energie entnommen wird. DSP-Cores wurden von Grund auf dafür entwickelt und verfeinert, die Echtzeitverarbeitung ohne nicht-deterministische Unterbrechungen zu unterstützen. Allerdings hegen die Konsumenten zusätzlich die Erwartung, dass die Informationen nicht nur in Echtzeit zur Verfügung stehen, sondern auch eine sinnvolle Zusammenfassung der Daten enthalten. Einen weiteren Aspekt der Analyse stellt neben der Latenz die eigentliche Auswertung der Daten dar. Zur Verringerung des Stromverbrauchs muss ein Gerät seine Daten nämlich in möglichst kurzer Zeit verarbeiten. Da diese Datenverarbeitung in der Regel mathematische Berechnungen erfordert, ist eine Architektur idealerweise so konzipiert, dass sie die schnelle Parallelverarbeitung mehrerer Befehle mit hoher Recheneffizienz zulässt. Eine DSP-Architektur erreicht beides durch die Verwendung von SIMD-Operationen (Single-Instruction, Multiple-Data) und von hocheffizienten Multiply-Accumulate-Operationen. SIMD-Operationen ermöglichen einen hohen Grad an Parallelität, da sie ein und denselben Algorithmus gleichzeitig auf mehrere Datenpunkte anwenden können, was die Verarbeitungszeit des Algorithmus verkürzt. Dies wiederum senkt die aktive Leistungsaufnahme und verlängert damit die Batterielebensdauer. Zahlreiche Algorithmen zur Analyse von Daten aus der realen Welt sind in hohem Maß auf die Umwandlung eben dieser Daten mithilfe von Filtern und Transformationen (z. B. FIR, FFT und DCT) angewiesen. Filter und Transformationen aber reduzieren sich mathematisch gesehen auf Summierungen von Multiplikationen, die sich mit Multiply-Accumulate-Operationen entscheidend beschleunigen lassen. DSP-Cores sind eigens für diese Multiply-Accumulate-Funktionen ausgelegt und liegen hier deshalb hinsichtlich der Performance an der Spitze. Ähnlich wie bei den SIMD-Operationen tragen auch Multiply-Accumulate-Funktionen dazu bei, die Verarbeitungszeiten zu verkürzen und die aktive Leistungsaufnahme zu verringern.

Äußere Aspekte von DSP-Architekturen

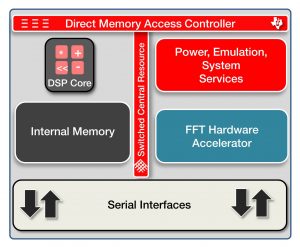

Der DSP-Core, der die Hauptlast der Verarbeitung übernimmt, kann durch die ihn umgebende SoC-Architektur entscheidend entlastet werden. Rechen-Effizienz erfordert zuverlässige Konnektivität in den Baustein hinein und ein zügiges Datenmanagement innerhalb des Bausteins. Ein gut durchentwickeltes DSP-SoC kann die Batterielebensdauer zusätzlich verlängern, indem es die Konnektivität und die Datenflüsse rationeller gestaltet. Die Konnektivität ist von höchster Bedeutung für Analysefunktionen in der Industrie und in Wearables für den Consumer-Markt, da die verwendeten Algorithmen auf externe Daten angewiesen sind, die dem Baustein somit von außen zugeführt werden müssen. DSP-SoCs verfügen deshalb meist über Schnittstellen, die wenig Verarbeitungsaufwand verursachen und kurze Latenzzeiten aufweisen und mit denen sich Daten schnell einlesen lassen (z. B. SPI, I²C und SRIO). Die hierdurch ermöglichten kurzen Übertragungszeiten verlängern die Batterielebensdauer, während die seriellen Protokolle gleichzeitig den Pin-Count und den Platzbedarf reduzieren. DSP-SoCs können die Steigerung der Performance und die Senkung der Stromverbrauchs jedoch noch auf einem weiteren Weg erzielen, nämlich durch die Verwendung chipintegrierter Beschleuniger, die für die Verarbeitung häufig vorkommender Aufgaben optimiert sind. Der DSP-Core kann während dieser Zeit entweder im Leerlauf bleiben oder andere Aufgaben ausführen. In einem DSP des Typs C5517 von Texas Instruments zum Beispiel ist die FFT-Funktion (Fast Fourier Transform) ein entscheidender Bestandteil des Algorithmus zum Extrahieren nützlicher Informationen beispielsweise für die Audioverarbeitung oder die Spracherkennung. Zur Senkung der Leistungsaufnahme ist der C5517 mit einem chipinternen FFT-Beschleuniger ausgerüstet, der die Effizienz gegenüber anderen Architekturen wie dem Cortex-M4 um ein Vielfaches verbessern kann.