Prüfvorrichtung für LDOs

Gemäß dem Schaltplan der Prüfvorrichtung in Bild 4 wird der für netzseitige Transienten vorgesehene Eingang mit einem Funktionsgenerator verbunden. Da dieser keine besonders hohen Ströme liefern kann, wird der in den Eingang eingespeiste Strom mit einem Emitterfolger verstärkt. An den Ausgang dieses Emitterfolgers ist ein 9-O-Widerstand angeschlossen, damit der Eingangskondensator während der Abfallzeit der eingangsseitigen Netztransiente zügig entladen wird. Für Tests, die keine Netztransiente erfordern, wird an diesen Eingang, der zum Eingang des LDO führt, eine konstante Gleichspannung gelegt. Der Enable-Eingang (EN) dient dazu, einen Impuls für die Anlaufprüfung mithilfe eines Funktionsgenerators bereitzustellen. In anderen Tests wird an den EN-Pin für die reguläre Enable-Funktion eine konstante Gleichspannung gelegt. Der Lasttransienten-Eingang wird ebenfalls von einem Funktionsgenerator angesteuert, der zur Durchführung eines Lasttransienten-Tests den NMOS fortlaufend schaltet. An den Ausgang des LDO ist stets eine Grundlast (1mA im Fall des LDO) angeschlossen, die jedoch bei Bedarf abgeklemmt werden kann. Drei weitere ohmsche Lasten werden mithilfe von Relais geschaltet. Mithilfe eines USB-Relaiscontrollers werden diese Relais von einem Computer aus gesteuert.

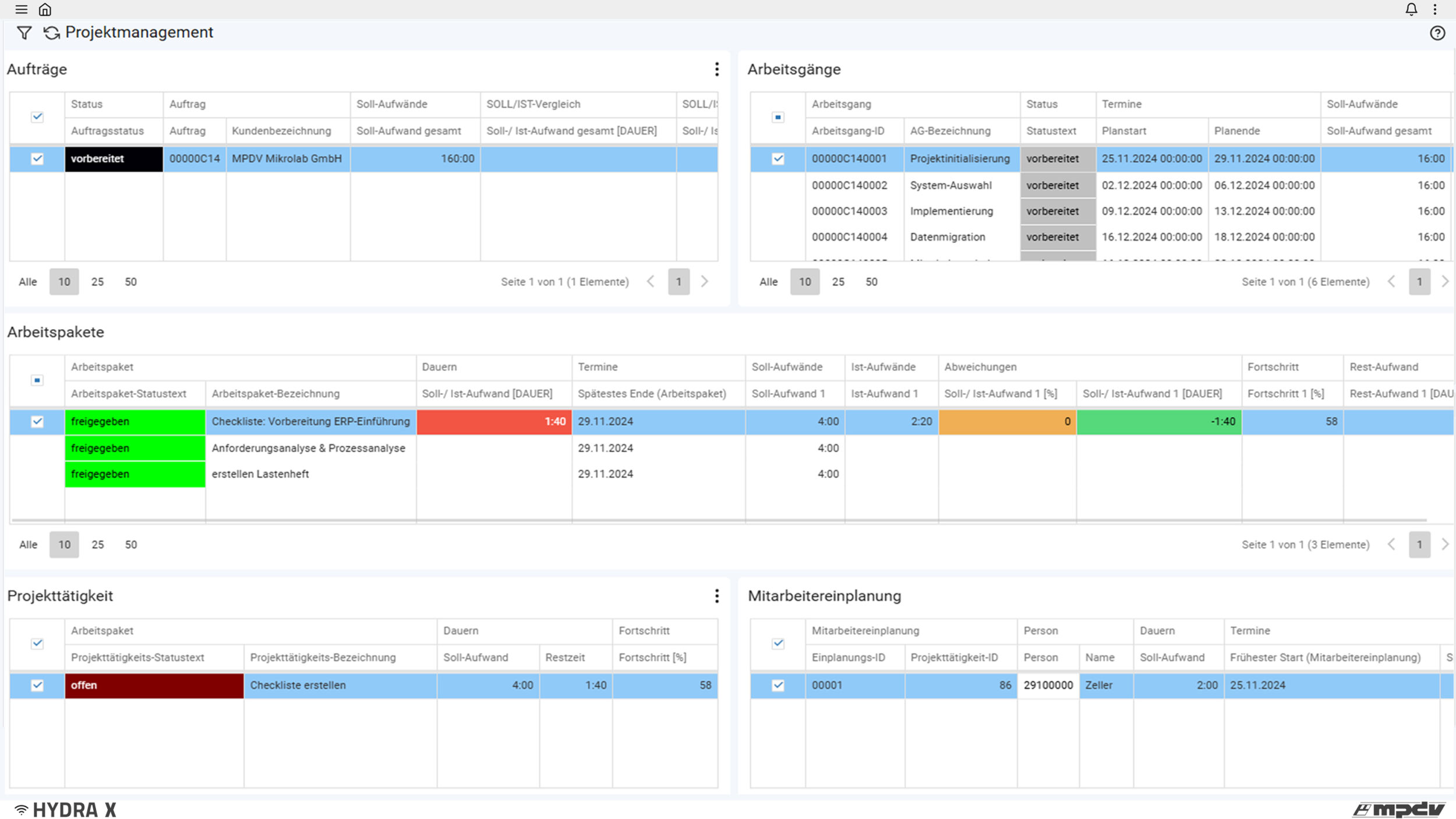

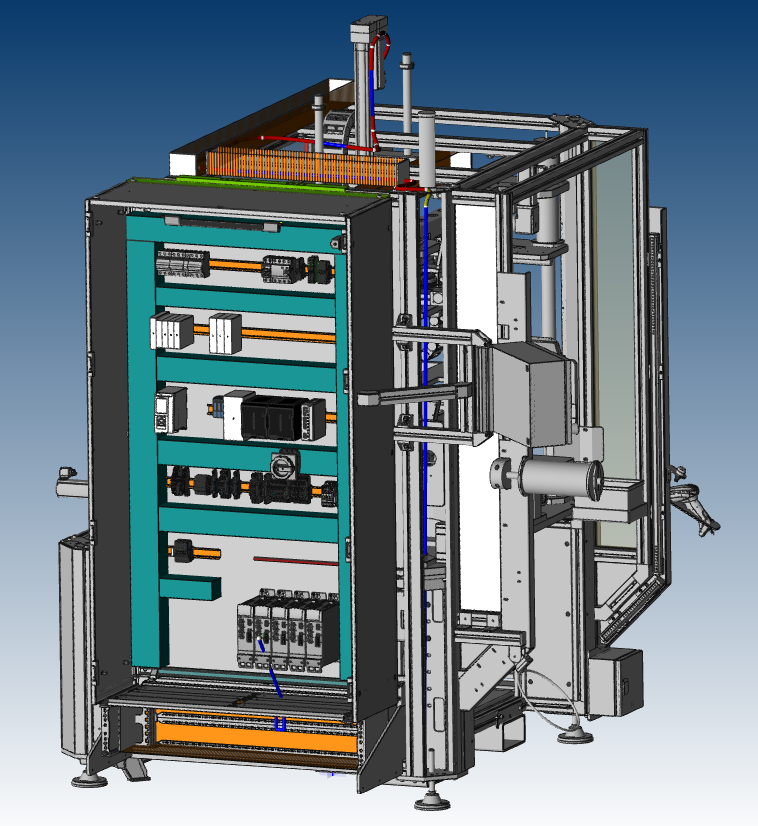

Prüfvorrichtung für Abwärtswandler

Die in Bild 7 gezeigte Prüfarchitektur für Abwärtswandler stimmt im Wesentlichen mit derjenigen für LDOs überein. Die einzige größere Modifikation besteht in drei zusätzlichen Relais. Diese wurden wegen der für ein Abwärtswandler-IC erforderlichen komplexen Lasttransienten-Prüfungen hinzugefügt. Anders als bei einem LDO erfordern die Lasttransienten-Tests bei einem Buck-Wandler unterschiedliche Grundströme. Für einen LDO werden beispielsweise Lasttransienten von 1mA auf 20mA, von 1mA auf 100mA und von 1mA auf 250mA benötigt, während die verschiedenen Lasttransienten-Prüfungen für einen Abwärtswandler Sprünge von 1mA auf 50mA, von 50mA auf 400mA, von 200mA auf 400mA und von 0,6A auf 1A erfordern. Hieraus erklärt sich die größere Anzahl Relais. Änderungen bestehen ebenfalls beim Leiterplattendesign. Da es sich bei dem Buck-Wandler um einen Schaltregler handelt, muss ein zusätzlicher Schalt-Pin abgetastet werden. Dieser Anschluss ist durch einen Abstand von 20mm an beiden Seiten der Leiterbahn und des Pins von den übrigen Teilen der Leiterplatte getrennt. Die Tests für die Buck-Prüfvorrichtung entsprechen exakt jenen für die LDO-Plattform.

Überlegungen zum Leiterplatten-Design

Es gibt zwei wichtige Überlegungen zum Layout der überarbeiteten, automatisierten Testplattform für die leistungsfähige Validierung. Zum einen geht es um die Wahrung der hohen Flankensteilheit und der Signalintegrität der Ansteuersignale. Hierzu ist die Prüfvorrichtung so ausgelegt, dass der Prüfling mit schnellen Netz- und Lasttransienten beaufschlagt werden kann. Impedanz-Unstimmigkeiten und Übersprechen zwischen den Leiterbahnen können diese schnellen Signalleitungen jedoch erheblich beeinträchtigen. Zum anderen geht es um die Spannungsabfälle an langen Stromversorgungs-Leiterbahnen. Insgesamt ist ein sorgfältiges Leiterplatten-Design unter Beachtung der Regeln für gute HF-Eigenschaften erforderlich. Notwendig ist es ebenfalls, die Signale möglichst nah an ihrem Ursprung zu messen, um Spannungsabfälle und parasitäre Effekte zu minimieren.