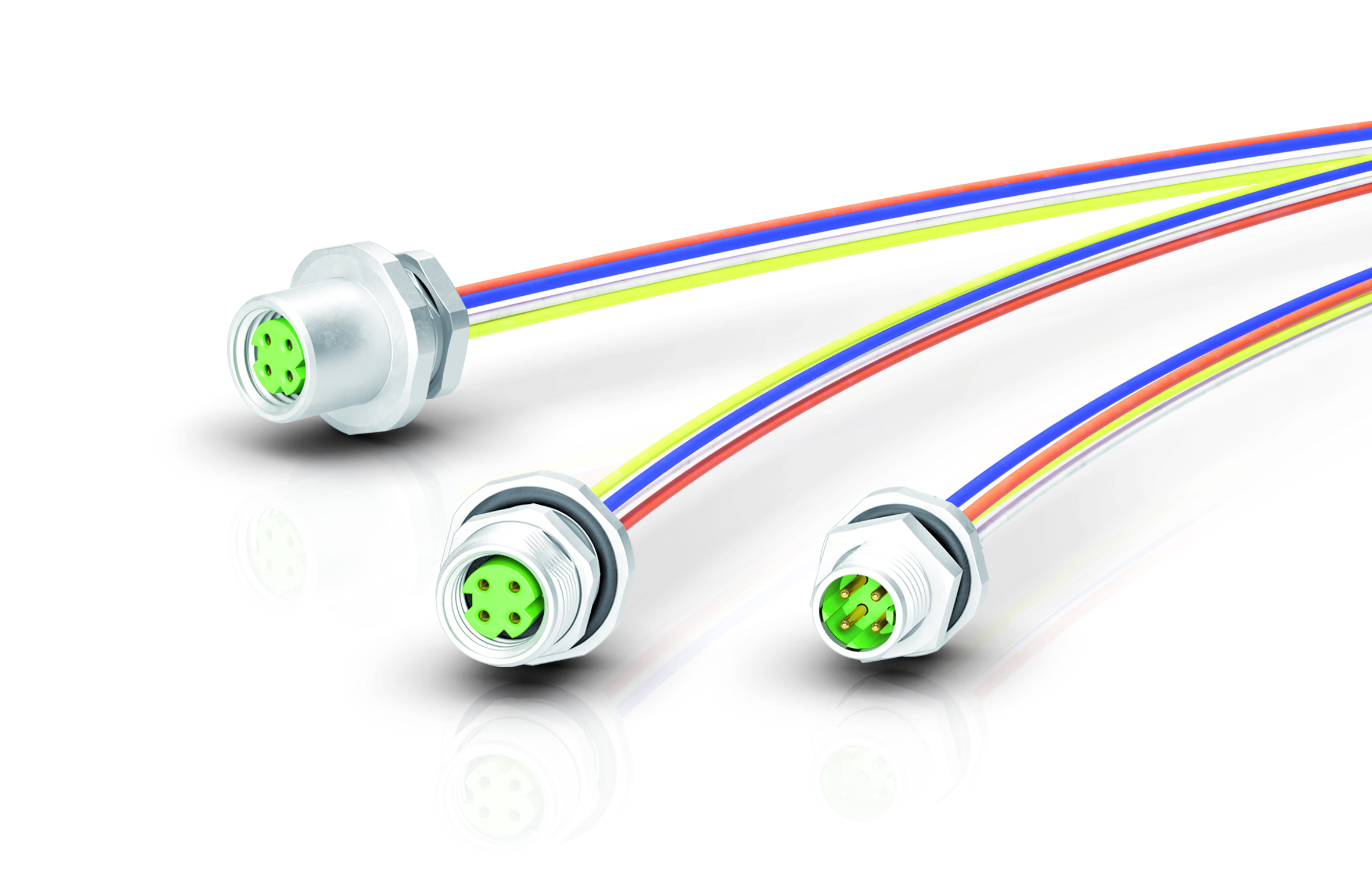

Mikrochip-Alterung per Knopfdruck vorhersagen

Das Wissen über Alterungsvorgänge in elektronischen Komponenten ist für viele Einsatzgebiete integrierter Schaltungen (ICs) entscheidend. Mit der zunehmenden Miniaturisierung von Mikrochips und neuen Fertigungstechnologien wird diese Aufgabe allerdings zu einer besonders großen Herausforderung. Forscher des Fraunhofer IIS/EAS haben deshalb speziell für diese Einsatzgebiete effiziente mathematische Modelle zur Vorhersage der Alterung von Transistoren entwickelt. Mit ihnen erhalten Elektronikdesigner weltweit erstmals die Möglichkeit, wirklichkeitsgetreue Simulationen durchzuführen und damit das Verhalten von Schaltungen auf Jahre im Voraus exakt zu prognostizieren. Die Alterungsmodelle beinhalten die typischen Effekte Hot Carrier Injection (HCI) und Bias Temperature Instability (BTI). Bei Bedarf können sie um weitere Effekte, wie Elektromigration (EM) ergänzt werden. Das Angebot des Fraunhofer IIS/EAS erweitert den üblichen Stand der Technik, indem es auch komplexere Abhängigkeiten abdeckt, zum Beispiel das Sättigungsverhalten über die Lebensdauer oder spannungsabhängige Zeitexponenten, die bislang nicht in den verschiedenen Design-Softwares verfügbar sind. »Wir bieten unseren Kunden erstmals die Möglichkeit, die Funktion kompletter elektronischer Systeme unter verschiedenen Nutzungsbedingungen zu verifizieren und zu validieren. So können sie sicher sein, dass ein Schaltkreis auch unter schwierigen Umgebungs- und Einsatzbedingungen zuverlässig funktioniert. Und das ohne kostspieliges ›Over Design‹ oder die Gefahr, dass es zu unerwarteten Ausfällen während des Betriebes kommt.« stellt Roland Jancke heraus, der am Fraunhofer IIS/EAS die Abteilung für Entwurfsmethoden leitet.

Fraunhofer-Institut für Integrierte Schaltungen IIS, Institutsteil Entwicklung Adaptiver Systeme EAS www.eas.iis.fraunhofer.de